JK-триггер

Символ JK-триггера с дополнительными асинхронными входами S и R,

аналогично представлению в среде разработки Altera

Quartus

| J |

K |

Q(t) |

Q(t+1) |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

0 |

JK-триггер[11][12]

работает так же как RS-триггер, с одним лишь исключением: при подаче

логической единицы на оба входа J и K состояние выхода триггера

изменяется на противоположное. Вход J (от англ. Jump

— прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill

— убить) аналогичен входу R у RS-триггера. При подаче единицы на

вход J и нуля на вход K выходное состояние триггера

становится равным логической единице. А при подаче единицы на вход K

и нуля на вход J выходное состояние триггера становится равным

логическому нулю. JK-триггер в отличие от RS-триггера не имеет

запрещённых состояний на основных входах, однако это никак не помогает

при нарушении правил разработки логических схем. На практике применяются

только синхронные JK-триггеры, то есть состояния основных входов J

и K учитываются только в момент тактирования, например по

положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как

можно видеть в таблице истинности JK-триггера, он переходит в инверсное

состояние каждый раз при одновременной подаче на входы J и K

логической 1. Это свойство позволяет создать на базе JK-триггера

Т-триггер, объединив входы J и К[13].

Символ D-триггера с дополнительными асинхронными входами S и R

| D |

Q(t) |

Q(t+1) |

| 0 |

0 |

0 |

| 0 |

1 |

0 |

| 1 |

0 |

1 |

| 1 |

1 |

1 |

D-триггер (D от англ. delay

— задержка)[14][15]

— запоминает состояние входа и выдаёт его на выход. D-триггеры имеют,

как минимум, два входа: информационный D и синхронизации С.

Сохранение информации в D-триггерах происходит в момент прихода

активного фронта на вход С. Так как информация на

выходе остаётся неизменной до прихода очередного импульса синхронизации,

D-триггер называют также триггером с запоминанием информации или

триггером-защёлкой. Рассуждая чисто теоретически, D-триггер можно

образовать из любых RS- или JK-триггеров, если на их входы одновременно

подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так,

например, для снятия 32 бит информации с параллельной шины, берут 32

D-триггера и объединяют их входы синхронизации для управления записью

информации в защёлку, а 32 D входа подсоединяют к шине.

Изображение T-триггера на схемах.

Работа схемы T-триггера (при T=1) на базе восьми 2И-НЕ логических вентилей. Слева — входы,

справа — выходы. Синий цвет соответствует 0, красный — 1

| T |

Q(t) |

Q(t+1) |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Т-триггер[16][17]

по каждому такту изменяет своё логическое состояние на противоположное

при единице на входе Т, и не изменяет выходное состояние при нуле

на входе T. Т-триггер часто называют счётным триггером.

Т-триггер может строиться как на JK, так и на D-триггерах. Как можно

видеть в таблице истинности JK-триггера, он переходит в инверсное

состояние каждый раз при одновременной подаче на входы J и K

логической 1. Это свойство позволяет создать на базе JK-триггера

Т-триггер, объединяя входы J и К. Наличие в D-триггере

динамического С входа позволяет получить на его основе T-триггер. При

этом вход D соединяется с инверсным выходом, а на вход С подаются

счётные импульсы. В результате триггер при каждом счётном импульсе

запоминает значение  ,

то есть будет переключаться в противоположное состояние. ,

то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на

Т вход подают единицу, а на С — сигнал с частотой,

которая будет поделена.

[править]

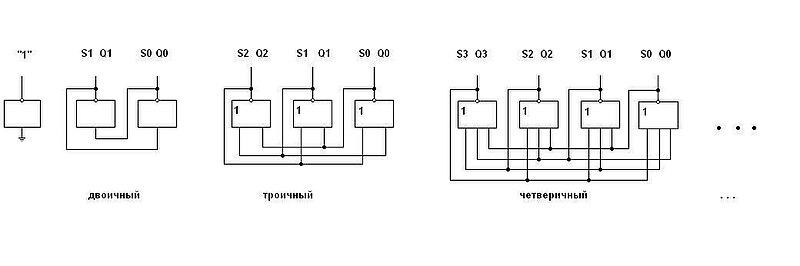

Триггеры

с любым числом устойчивых состояний

Триггер с любым числом устойчивых состояний N строится из N

логических элементов (N-1)ИЛИ-НЕ или (N-1)И-НЕ путём соединения выхода каждого элемента

(Q0, Q1, …, Q(N-1)) с соответствующими входами всех других элементов. То

есть наименьшее число логических элементов для построения N-ичного

триггера равно N.

Триггеры на элементах (N-1)ИЛИ-НЕ работают в прямом одноединичном

коде (на выходе Q одного из элементов — «1», на выходах Q других

элементов — «0»).

Триггеры на элементах (N-1)И-НЕ работают в инверсном однонулевом коде

(на выходе Q одного из элементов — «0», на выходах Q других элементов —

«1»).

При добавлении N транзисторов доступа эти триггеры могут работать как

ячейки статической сверхоперативной памяти (SRAM).

При добавлении схем управления переключением эти триггеры могут

работать как N-ичные аналоги двоичного RS-триггера.

В непозиционных системах счисления:

удельные затраты инверторов от числа состояний триггера не зависят:  ,

где x1 - число инверторов, x2 - число состояний триггера. ,

где x1 - число инверторов, x2 - число состояний триггера.

Удельные затраты диодов в логических частях логических элементов от

числа состояний триггера имеют линейную зависимость:  ,

где x1 - число инверторов, x2 - число состояний триггера, (x2-1) -

число диодов в логической части одного логического элемента. По этому

параметру выгоднее двоичные триггеры. ,

где x1 - число инверторов, x2 - число состояний триггера, (x2-1) -

число диодов в логической части одного логического элемента. По этому

параметру выгоднее двоичные триггеры.

В сдвоенных

показательных позиционных

системах счисления:

по теореме Джона фон Неймана [18]

из целочисленных систем счисления наибольшим удельным числом

представимых чисел и наименьшими аппаратными затратами обладают троичные триггеры,

второе место занимают двоичные и четверичные триггеры.

|